General

VHDL

- Design Unit

- Entity

- Architecture

- Package

- Delta Delay

VSIM 13> cd hdl/simulation/questa VSIM 13> pwd hdl/simulation/questa VSIM 13> do ../scripts/do_all.do

|

Summary: History of VHDL

| 1981 | Initiated by US DoD to address hardware life-cycle crisis |

| 1983-85 | Development of baseline language by Intermetrics, IBM and TI |

| 1986 | All rights transferred to IEEE |

| 1987 | Publication of IEEE Standard |

| 1987 | Mil Std 454 requires comprehensive VHDL descriptions to be delivered with ASICs |

| 1994 | Revised standard (named VHDL 1076-1993) |

| 2000 | Revised standard (named VHDL 1076 2000, Edition) |

| 2002 | Revised standard (named VHDL 1076-2002) |

| 2007 | VHDL Procedural Language Application Interface standard (VHDL 1076c-2007) |

| 2009 | Revised Standard (named VHDL 1076-2008) |

modelsim.ini Variables

Explicit

This variable enables the resolving of ambiguous function overloading in favor of the “explicit” function declaration (not the one automatically created by the compiler for each type declaration). Using this variable makes QuestaSim compatible with common industry practice.

You can override this variable by specifying vcom -explicit.

Specifying Resource Libraries

Note that the library clause is not used to specify the working library into which the design unit is placed after compilation. The vcom command adds compiled design units to the current working library. By default, this is the library named work. To change the current working library, you can use vcom -work and specify the name of the desired target library.

Compiling a VeriLog Design

VSIM 13> vlog [...]

Compiling a VHDL Design

For VHDL, the order of compilation is important. You must compile any entities or configurations before an architecture that references them.

VSIM 13> vcom -2002 -explicit -work ../questa/work ../source/top_tb.vhd -2002 Revision VHDL 1076-2002 -explicit Enables the resolving of ambiguous function overloading -work <directory> Specify the name of the desired target library <source> VHDL source

Built-in Libraries and Packages

In most vhdl programs you have already seen examples of packages and libraries. Here are two:

library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_signed.all;

The packages are std_logic_1164 and std_logic_signed and the library is ieee. Since the scope of the library statement extends over the entire file, it is not necessary to repeat that for the second package.

It’s instructive to show where the packages are physically located. For Altera Max+2 and Xilinx Foundation these locations typically are:

Altera: ~\maxplus2\vhdl93\ieee\std1164.vhd Xilinx: ~\fndtn\synth\lib\packages\ieee\src\std_logic_1164.vhd

It is thus tempting to come to the conclusion that the “library ieee;” statement indicates the “directory” in which the std_logic_1164 package is located. Note, however, where it is in Synplicity:

Synplicty: ~\synplcty\LIB\vhd\std1164.vhd

In the latter there is no mention of ieee at all. It is thus more appropriate to think of ieee as a pointer to the location of the package. The directory structure shown in those three examples depicts the directories where the packages are loaded when the software is installed. The pointer ieee is hardcoded in the compilers and thus there is no need for the user to associate that pointer with the directory structure, nor is it possible to put the packages anywhere else after the software has been loaded.

User Libraries and Packages

User libraries and packages are setup very similarly to the built-in ones. However, in that case, the user is responsible for the directory structure, the contents of the files, etc. Note that the user must then also set up the pointer to the package. The following shows a complete example of this arrangement. There are two ways to do this: 1) with the “work” directory; 2) with a user library.

Libraries and Packages in VHDL

WORK is not a VHDL Library

WORK is not the name of a VHDL library. This may surprise some (or even most) VHDL designers, even experienced engineers. Most of the time, nobody gets bothered by this. But on occasion, it can cause great confusion and waste of time.

All knowledge about VHDL starts with the IEEE Standard VHDL Language Reference Manual. LRM for short. Not much is said about “WORK”, but in section 11.2 (in the LRM 1076-2000) you can read the following:

Every design unit [...] is assumed to contain the following implicit context items [...]: library STD, WORK; use STD.STANDARD.all; [...] Library logical name WORK denotes the current working library during a given analysis.

Let me repeat: WORK denotes the current working library.

This means that there is no library named WORK. Instead, the identifier WORK just refers to the current library. You can compare WORK with the Java concept of this. In Java this refers to this object, which obviously is different for each object. This makes me think of a silly joke of man who asks: “is this the second street to the right?”

Enough silliness. Much confusion comes from the fact that VHDL tools allow you to give the name “WORK” to a library:

vlib work vcom -work work myfile.vhd

That is as crazy as having a street address of John Doe, Ourstreet, MyHomeTown. How will your mail ever get there? And that is exactly the problem with using WORK as a library name. Other libraries cannot refer to you. If another library (say alex) they would refer to work.yourpackage.all, the VHDL analyser would read this as the alex.yourpackage.all.

It would have been better if VHDL tools would refuse the explicit name of WORK for a library. It would have been better if WORK were a reserved keyword in VHDL. But hey, there is no way to change that now. The best you can do is be aware of this idiosyncrasy in VHDL and live with it. Preferably by avoiding WORK all together.

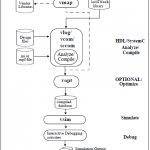

Simulating a VHDL Design

A VHDL design is ready for simulation after it has been compiled with vcom and possibly optimized with vopt. You can then use the vsim command to invoke the simulator with the name of the configuration or entity/architecture pair or the name you assigned to the optimized version of the design.

VSIM 13> vsim -novopt -t 1ps -lib work work.top_tb -novopt Simulate without Optimization -t <time> Override Resolution Limit -lib

Simulator Resolution Limit

vsim -t 10ps topmod

In the example above, a delay of 4 ps would be rounded down to 0 ps, and a delay of 6 ps would be rounded up to 10 ps.

Examining and Setting Signals and Variables with commands

VSIM> examine -time 13710 ns -radix hex /top_tb/DUT/ata_block_i # 0EEDFA9A994350F07214CA6151823A08 VSIM> change /top_tb/DUT/ata_block_i 00000000000000000000000000040002

FAQ

Question

# ** Error: (vcom-11) Could not find work.aes_tb_package. # ** Error: ../tb/aes_tester.vhd(54): (vcom-1195) Cannot find expanded name "work.aes_tb_package". # ** Error: ../tb/aes_tester.vhd(54): Unknown expanded name. # ** Error: ../tb/aes_tester.vhd(56): VHDL Compiler exiting # ** Error: /opt/questasim_10.1d/questasim/linux/vcom failed.

Answer

Compile other VHDL file first!

Question

# vsim -lib work -t 1ns -novopt work.aes_tester # ** Error: (vsim-19) Failed to access library 'work' at "work". # No such file or directory. (errno = ENOENT) # Error loading design # Error: Error loading design # Pausing macro execution

Answer

Change to questa directory or map it like this:

vlib ../questa/work vmap work ../questa/work