- Anki

- Notion

- Rome Research

- Obsidian

- RemNote

- Doppelt verlinkte Notizen

eDesign / Miniware TS100

eDesign / Miniware TS101

eDesign / Miniware TS80P

Pine64 Pinecil

|

|

|

|

TS100/TS101 Series Soldering Iron Tips

Nine modles: TS-B2 / BC2 / C4 / D24 / K / KU / I / ILS / C1

|

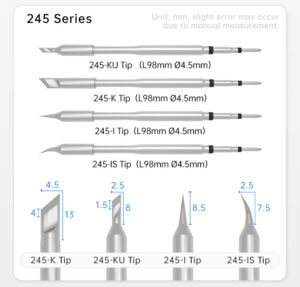

245 Series Soldering Iron Tips

Three modles: BC2, K, D24

|

210 Series Soldering Iron Tips

Three modles: KU, I, IS

|

|

|

|

|

|

Which USB C Soldering Iron is the Best for 2025? Pinecil vs Fnirsi vs TS101

Spiderman Cake Topper

minions cake topper

Pikachu – Zápich do dortu (Pikachu Cake Topper)

Groot – Zápich do dortu (Groot Cake Topper)

Bluey & Bingo – Zápich do dortu (Bluey & Bingo Cake Topper)

Malá mořská víla – Ariel a Šupinka (The Little Mermaid – Ariel & Flounder) – Zápichy do dortů / Cake Toppers

Sonic the Hedgehog Cake Topper (NO AMS-Multipart)

Hot Wheels cake topper

Harry Potter – Zápich do dortu (Harry Potter Cake Topper)

Cake topper with tractor and name – Jamie

Dirty dancing cake topper

“Davin is a Fast ONE” – cake topper

Breakdance Silhouette Cake Topper

Minie Topper Cake

Lion Topper Cake

Koala Topper Cake

Jednorožec s duhou (Unicorn & Rainbow) – Zápichy do dortů / Cake Toppers

Tlapková Patrola (PAW Patrol – Zuma and Marshall) – Zápichy do dortů / Cake Toppers

Baby Shark – Zápichy do dortu (Baby Shark Cake Toppers)

Hasiči – Zápichy do dortu (Firefighter Cake Toppers)

Bing & Flop – Zápichy do dortů (Bing & Flop Cake Toppers)

Dopravní značky – Zápichy do dortu (Traffic Sign Cake Toppers)

Hulk – zápich do dortu / Cake Toppers

Star Wars – Han Solo & Leia – Zápichy do dortů (Star Wars Han Solo & Leia Cake Toppers)

Timer PWM with DMA stops too early on STM32G431

The unused I/O pins should be configured as analog input by software; they should also be connected to a fixed logic level 0 or 1 by an external or internal pull-up or pull-down.

Recommended course of action for Unused pin of STM32 MCU

Pin value of a GPIO pin set as high impedance

GPIO outputs are in high-impedance state

Because it’s an “at-least-N-ms” delay with 1ms granularity.

HAL_Delay works and doesn’t work

Is HAL_Delay(1) quaranteed to be close to 1ms?

HAL_Delay(1); takes 2ms

It takes 2 mins to generate PWM signal in STM32

STM32 Guide #3: PWM + Timers

STM32 LESSON #5: TMER (PWM + DMA)

Confusion about length parameter in HAL_TIM_PWM_Start_DMA

Interface WS2812 with STM32

github.com/MaJerle/stm32-ws2811-ws2812-ws2812b-ws281x-tim-pwm-dma-timer

Improved STM32 WS2812B DMA library

Tutorial: Adafruit WS2812B NeoPixels with the Freescale FRDM-K64F Board – Part 5: DMA

STM32G0 Boot0 und SWCLK selber Pin

STM32G030 BOOT0 versus SWD

STM32G030 BOOT0 pin – SWCLK

STM32G0 Series Workaround for BOOT0-Pin Problem #82

AN5096 – Application note – Getting started with STM32G0 Series hardware development (PDF)

RM0454 – Reference manual – STM32G0x0 advanced Arm-based 32-bit MCUs (PDF)

| a |

| b |

| c |

PPTC = Polymeric Positive Temperature Coefficient Device

PTC = Positive Temperature Coefficient Device

NTC = NegativeTemperature Coefficient Device

PPTC Self-Recovery Fuses, 250V

PPTC Resettable Fuse, 250V, TRF250-500

The Best Protection for your Circuit is NOT a Fuse!…..but a Resettable Fuse? EB#54

The Best Protection for your Circuits? eFuse! Here is why they are awesome! EB#48

NCP1010: Self-Supplied Monolithic Switcher for Low StandbyPower Offline SMPS (PDF)

Flyback vs. Buck: Which to Use for DC/DC Conversion?

Instructable: DIY Buck/Boost Converter (Flyback)

elements14: A Noise-Free DIY Switching Power Supply – How Hard Can It Be? — Episode 542

DC Power: DC-to-DC Converters

How Buck, Boost & Buck-Boost DC-DC Converters Work

How does a modern Power Supply work?! (230V AC to 5/12V DC) DIY Flyback Converter!

Every Component of a Switch Mode Power Supply Explained

Every Component of a Linear Power Supply Explained (while building one)

Understanding Switching Mode Power Supplies

A Noise-Free DIY Switching Power Supply – How Hard Can It Be?

How SMPS works | What Components We Need? Switched Mode Power Supply

#772 Basics: Switching Power Supplies (part 1 of 2)

Howto repair switch mode power supplies #1: basics, and block diagram of a PSU

Switching Regulator PCB Design – Phil’s Lab #60

The SM7035P is an adjustable step-down DC-DC converter. It works by converting a DC input voltage to a lower, adjustable DC output voltage, typically between 3.3V and 18V. This conversion is achieved through a series of switching actions within the converter, which effectively “steps down” the voltage while providing a stable output.

Here’s a more detailed breakdown: